研究内容

3D集積/チップレット

先端半導体においてひとつの指標とされてきた、微細化則(ムーアの法則)による高集積化、低消費電力化を達成するための開発投資コスト、設計最適化が問題となっています。

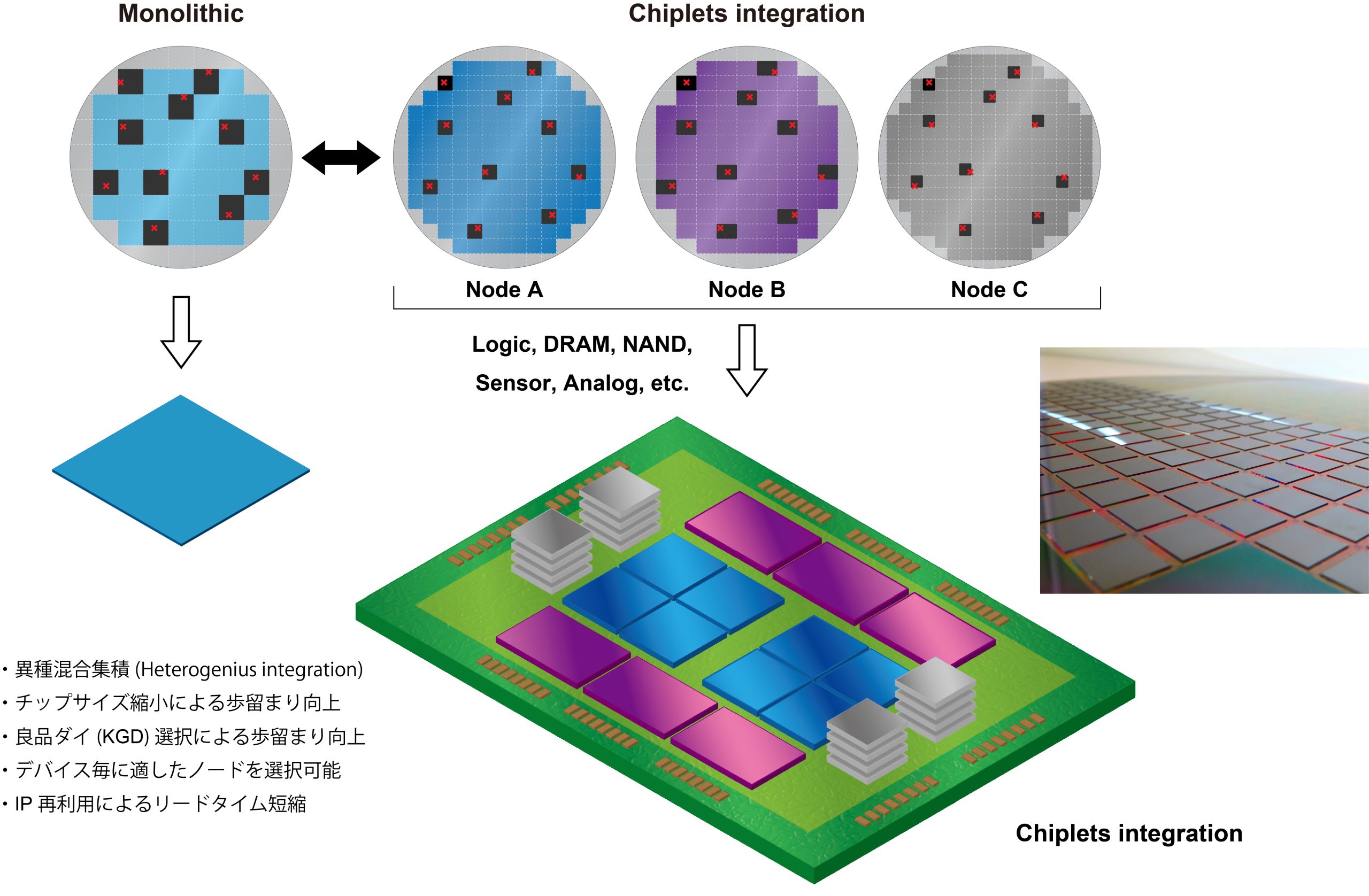

これらの現状を打破する設計思想、集積技術が、「チップレット」です。必要な機能を分割し適切な技術ノードで高歩留まりにて製造し、半導体後工程の組み立て技術によって接続・パッケージをすることで高集積化、Time to Marketの短縮、配線最適化による低消費電力化が達成可能な技術とされています。

チップレットの基本的なコンセプトは、ダイ(チップ)の一面にすべての要素を作り込む(=モノリシック)のではなく、さまざまコンポーネントを必要な技術ノードに沿って作り、それを後に組み立てて基板上の配線でつなげていくものです。

モノリシックのみで微細化による低消費電力化を進めるためには、多くの工程を繰り返さなければならず、さらにダイの面積が大きくなればなるほど不良が発生してしまいます。一方でチップレットであれば良品選別可能というだけではなく、配線の再設計や最適化も可能であり、エネルギー効率を非常に高くすることが可能となる。さらに小さなチップレットで作成し「つなぐ」ことによって、生産性と歩留まりが向上すると考えられています。

このようにチップレットそのものは技術的に特別な革新があるわけではないが、より経済的に低消費電力の半導体を製造し、数多の需要を満たすには、この設計/製造のコンセプトなしでは不可能となりつつあります。

3Dヘテロデバイス

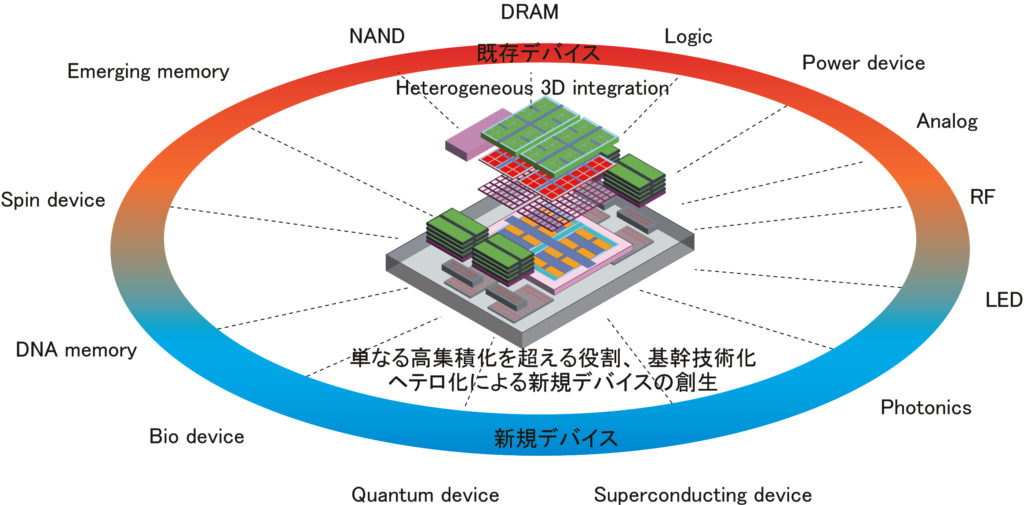

さらに2050年を見通すと自動運転等による輸送機器の自動化、Beyond 5G によるスマートシティ、 VR/ARによるデジタルサービス、オンライン診療による遠隔診療等これらすべてにおいて電子デバイスが重要な役割を担っています。こういった高度な最終アプリケーションの実現は単一デバイスの微細化による高集積化や高性能化のみでは達成できず、メモリ、ロジック、パワーデバイス、各種センサ、光デバイスなど様々なデバイスを高度に並行運用可能な「異種融合(ヘテロ)デバイス」が必要です。

本研究室ではこの3Dヘテロデバイスへ向けた「後工程プロセス技術」を中心に研究を行います。

主な研究テーマ

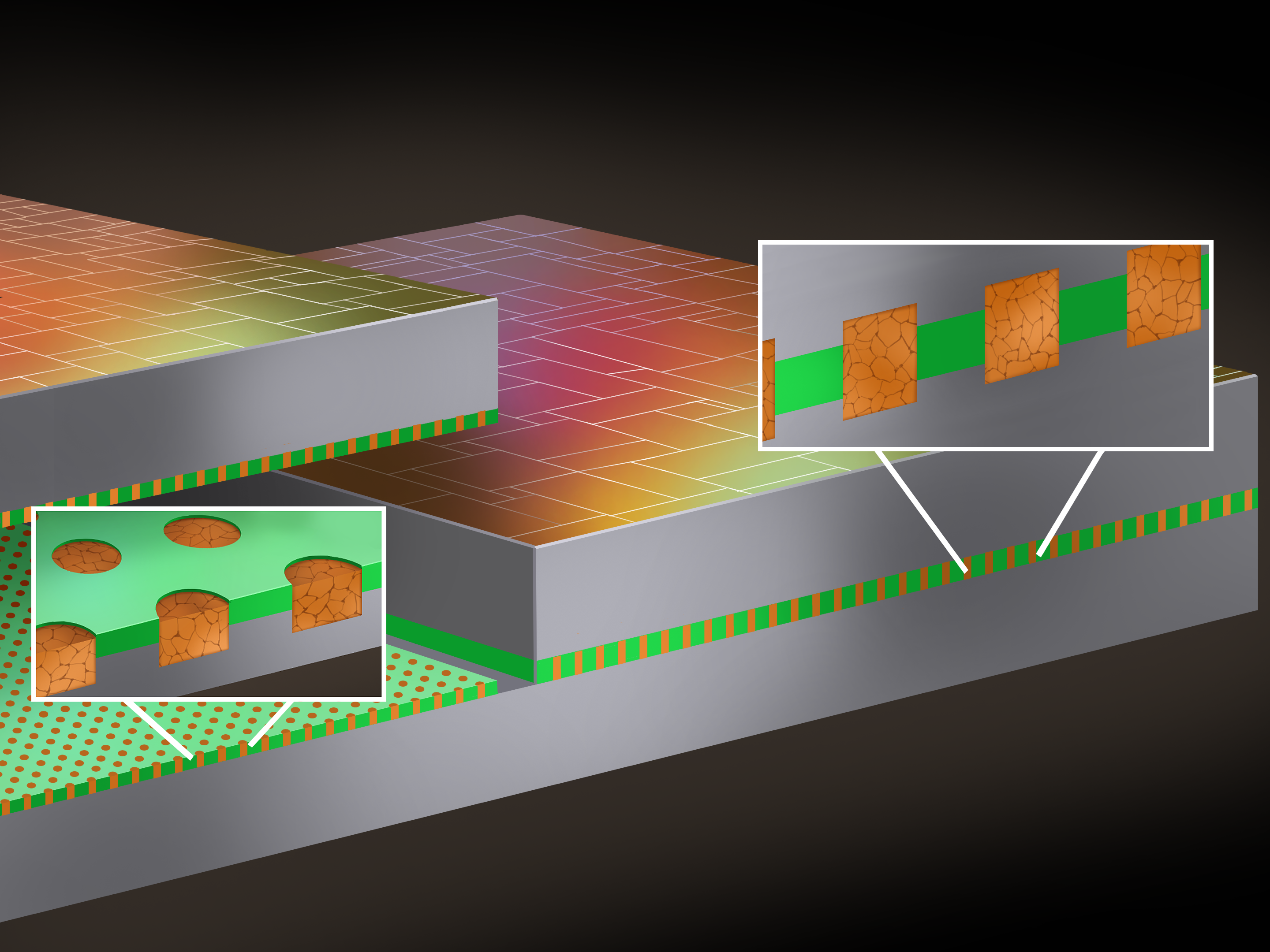

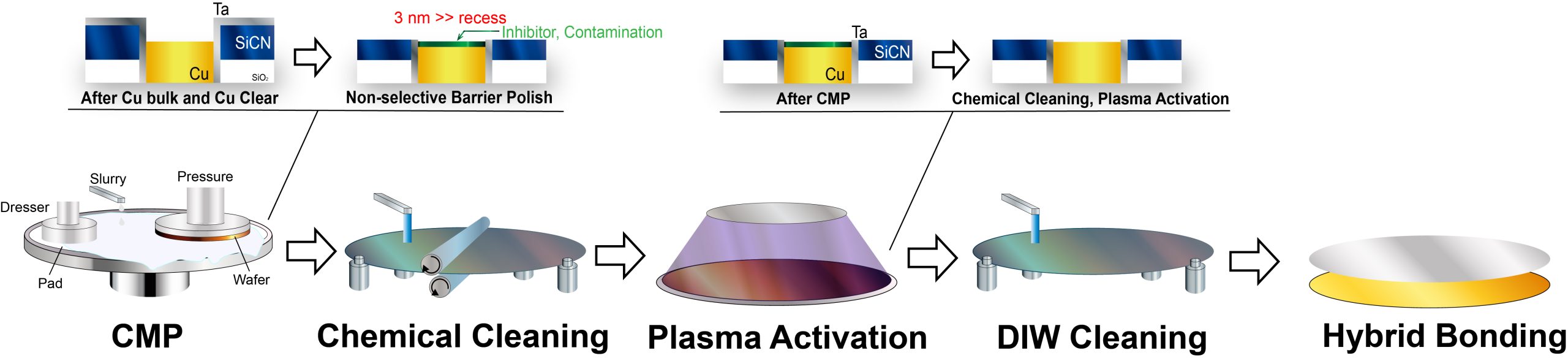

1.ハイブリッド接合

異種デバイスをウエハ上にて積層するWafer-to-Wafer接合技術では 、直接接合とVia-last TSV による接続からさらに発展し、現在ではよりデザイン自由度が高い「 Cu-SiCNハイブリッド接合」の熾烈な開発競争が起こっています。この技術はダマシン工程によって形成した接合面をプラズマ表面活性化により接合する、一度の接合で機械的な接合絶縁膜と電気的な接合金属を達成する手法です。さらにチップレット、3Dヘテロデバイスではダイサイズ不問、良品(KGD)選別が可能なDie-to-Wafer(D2W) 接合技術の開発が重要です。従来のD2W接合はスズ(ソルダー)の共晶反応を利用した熱圧着接合が使用されていますが、熱圧着接合では狭ピッチでの信頼性、アライメント精度の限界を迎えています。ここでも「ハイブリッド接合」を用いた接合ピッチ縮小のブレークスルーに向けて研究開発競争が進んでいます。

本研究室ではハイブリッド接合に向けた「めっき」、「CMP」、「直接接合」すべての研究を進める世界でも数少ない研究室です。さらにはプレアセンブリ技術(ダイシング、ダイレベル洗浄等) に関する研究も行っています。

2.化学機械研磨(CMP)

ハイブリッド接合の精度は、接合するウエハ表面の仕上がりによって大きく変化します。そのため、表面仕上げの役割を担うCMPという”研磨”は非常に重要です。CMP装置は、スラリーの化学的作用と研磨パッドの物理的作用で、ウエハと研磨パッドの間に入り込んだスラリー中の砥粒によって、ウエハを研磨する仕組みです。

ハイブリッド接合におけるCMP工程は大きくCu研磨、Cu除去、Ta除去&平坦化の三つに分けられ、現在、課題とされているのは、三つ目の工程であるTa除去と平坦化です。ここでいう平坦化とはCu、Ta、SICN膜を平坦にすることを指します。未調整の場合、CuはTaよりも電気化学的に活性な金属であるため、CuはTaよりも腐食されてしまい、リセスが発生してしまいます。逆に、腐食を抑制しすぎてしまうと、Cuの突出ができていしまいます。課題を解決するためには、Cu、Ta、SiCNの研磨選択比を最小化する必要があります。

さらにポストCMP洗浄や接合前の表面活性化においても、リセスを抑制することが非常に重要です。

これらを達成するために、電気化学測定、ゼータ電位測定、洗浄、プラズマ活性化、さらには実際の研磨を行って評価を進めています。

さらに今後はハイブリッド接合だけではなく、微細配線のポストCu材料における研磨にも挑戦する予定です。

3. Cuめっき

ハイブリッド接合においてはCuの結晶性や結晶粒のサイズも非常に重要です。これらの要因を決めるのはめっき工程です。新規な添加剤を用いて「Designer Cu」と呼ばれるハイブリッド接合に適したCu膜の形成を行っています。

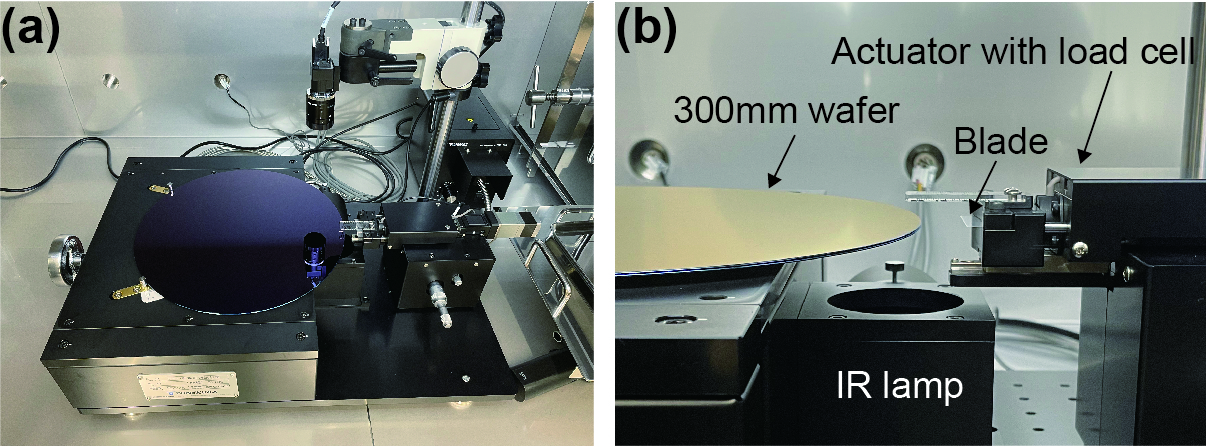

さらには集積技術や要素技術だけでなく、新規なチップレットでの「測定、評価手法」においても独自の観点から世界的にも必要とされる、今後の開発に不可欠な技術の開発を進めています。特に注力して評価を進めているのが、ハイブリッド接合での接合強度測定手法の開発です。W2Wハイブリッド接合ではDouble-Cantilever Beam(DCB)法と呼ばれる、カミソリを差し込むことによって接合強度を測定する手法が用いられています。この手法に関して、本研究室手動での国際規格化へ向けて研究を進めています。

さらにダイレベルの接合強度はボンダーやダイシングなどの装置開発においても必須の評価項目であり、新たな評価手法としてナノインデンテーションを用いた手法の開発を進めています。

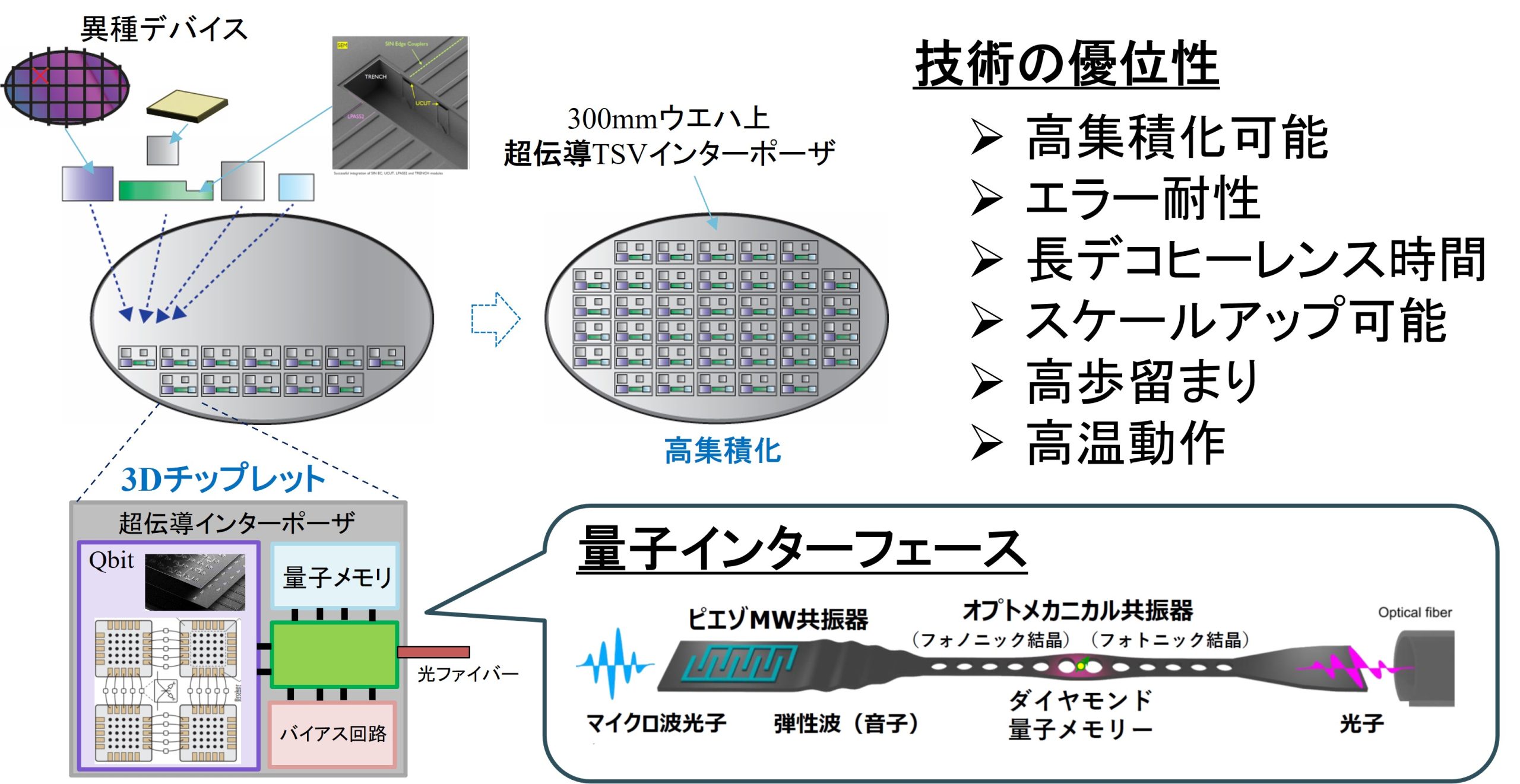

5.三次元量子コンピュータ集積技術

量子コンピュータにおいては量子ビットの並列数が量子演算の計算速度を決めており、その数が増えれば計算速度は指数関数的に増加します。将来的な量子ビットのスケールアップのためには、制御回路を量子ビットと集積化することが必須の技術となります。量子ビットと制御回路は別種の超伝導集積回路技術を用いるため、「異種デバイスの混載技術」が必要となります。また量子ビットのエラーコレクションのために、例えばサーフェイスコードが用いられるが、そのためにはマイクロ波回路との3D積層が必須です。これら量子ビットと他の演算回路、超伝導素子を別々に作成し、三次元実装技術によって接続する三次元量子コンピュータ (3D-QC) が大いに期待されています。

本研究室では超伝導TSV 、超伝導ハイブリッド接合などを研究し、この3D-QCの実現を目指します。